# Multilevel Inverter Using H-Bridge and Two-Level Power Modules

Suroso (University of Jenderal Soedirman), and Toshihiko Noguchi (Shizuoka University)

## 1. Introduction

Multilevel inverters have capability to deliver a multilevel AC waveform with low-rating devices, lower dv/dt or low di/dt, and a less-distorted output waveform resulting in reduction of harmonic losses, reduction of EMI noise and reduction of the output filter size [1], [2]. This paper presents a different topology of the multilevel voltage-source inverter obtained from an H-bridge inverter and two-level power modules. In the proposed topology, all of the DC power sources are connected in series, which has possibility of using non isolated DC voltage sources. The minimum number of the power devices and its modular structure are other features of the proposed topology. The proposed topology is tested and verified through computer simulations using a PSIM software and experimental tests. The computer simulation and experimental test results showed that the proposed topology works properly to synthesize a multilevel output waveform.

### 2. Circuit Configuration

Reference [3] presented a configuration of the multilevel inverter achieved by using series-connected sub-multilevel converter blocks with bidirectional power switches and an H-bridge inverter. Reference [4] proposed another multilevel inverter using an H-bridge inverter with auxiliary bidirectional power switches. However, in practical manner, the use of bidirectional power switches can be a main drawback. Bidirectional switches obtained by using two IGBTs or a combination of a single IGBT and four power diodes increase power losses of the inverter. Reference [5] presented another new configuration of the multilevel inverter from several two-level power cells. The need of isolated DC sources and a large number of power switches in this topology increase its cost and complexity of the inverter in case isolated rectifier circuits are used. Reference [6] presented a new symmetrical hybrid multilevel inverter using three-level cells and an H-bridge inverter. Eight power switches are required to construct even a five-level inverter.

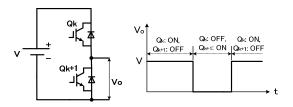

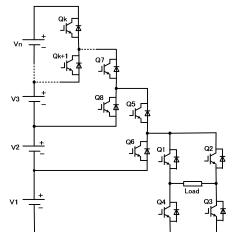

In this paper, a different configuration of the multilevel inverter using an H-bridge inverter and two-level power modules are presented. Fig. 1 shows the configuration of a basic two-level power module and its output waveform. The proposed multilevel inverter is obtained by connecting some two-level power modules and an H-bridge inverter as shown in Fig. 2. The DC voltage sources are connected in series, which makes it possible to use non isolated DC voltage sources. In addition to this advantage, all of the power switches are a single IGBT or power MOSFET, which is not a bidirectional switch. If N sets of two-level power modules are connected to the H-bridge inverter, the level number the output voltage waveform M can be expressed as:

| М | = 3 + | -2N. |  |  | (1) |

|---|-------|------|--|--|-----|

|   |       |      |  |  |     |

The number of the power switches *P* is:

$$P = 4 + 2N$$

.

The number of the capacitors or DC voltage sources C is:

$$C = N + 1. (3)$$

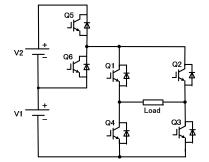

A five-level inverter circuit needs a single power module and an H-bridge inverter with only six power devices in total, as shown in Fig. 3. If the DC voltage sources of the five-level inverter are assumed to be the same as V/2, Table 1 lists the switching states of the proposed five-level inverter for five-level output voltage waveform generation, i.e. +V, +V/2, 0, -V/2 and -V.

Fig.1. Two-level power module and its output waveform.

Fig. 2. General topology of M-level inverter.

Fig. 3. Proposed five-level inverter.

Table 1. Switching states of proposed five-level inverter.

|   | <b>Q</b> 1 | <b>Q</b> <sub>2</sub> | <b>Q</b> <sub>3</sub> | Q4 | <b>Q</b> <sub>5</sub> | <b>Q</b> <sub>6</sub> | Output |

|---|------------|-----------------------|-----------------------|----|-----------------------|-----------------------|--------|

|   | 1          | 0                     | 1                     | 0  | 1                     | 0                     | +V     |

|   | 1          | 0                     | 1                     | 0  | 0                     | 1                     | +V/2   |

| ĺ | 0          | 0                     | 1                     | 1  | 0                     | 0                     | 0      |

| ĺ | 0          | 1                     | 0                     | 1  | 0                     | 1                     | -V/2   |

| ĺ | 0          | 1                     | 0                     | 1  | 1                     | 0                     | -V     |

(2)

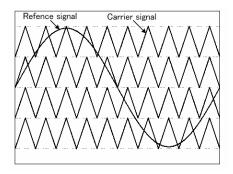

Fig. 4. Multi-carrier based sinusoidal PWM.

#### 3. Simulation and Experimental Test Results

The five-level inverter circuit shown in Fig. 3 is connected to an inductive load, i.e.  $R = 20 \ \Omega$ , L = 5 mH. The switching and the output voltage frequencies are 22 kHz and 60 Hz, respectively. The amplitude of the DC voltage sources V1 and V2 are equally 50 V. A triangular level-shifted carrier based sinusoidal pulse width modulation (PWM) strategy is used to generate the gating signals of the power switches and to obtain a lower distortion of the output waveforms as shown in Fig. 4. Fig. 5 shows a computer simulation result of the five-level inverter circuit. A proper five-level output waveform was generated by using the proposed strategy. A sinusoidal current also flows through the load without remarkable ripples. Furthermore, Fig. 6 shows the experimental waveforms of the five-level inverter showing a load voltage and a load current when the modulation index is 0.94. The voltages across the drain-source of the power switches Q5 and Q6 are also presented, of which the amplitudes are half of the five-level output voltage waveform.

#### 4. Conclusions

In this paper a new topology of the multilevel voltage-source inverter has been introduced. The proposed inverter uses a combination of two-level power modules and an H-bridge inverter for multilevel voltage waveform generation with the minimum number of power devices. Computer simulation and experimental test results of the single-phase five-level inverter prototype have proven feasibility of the proposed approach.

#### References

- M. Malinowski, K. Gopakumar, J. Rodriguez, and M. A. Pérez, "A survey on cascaded multilevel inverters", *IEEE Trans. On Industrial Electronics*, vol. 57, no. 7, p.p. 2197-2206, July 2010.

- [2] J. Rodiguez, J. S. Lai, and F. Z. Peng, "Multilevel inverter: a survey of topologies, controls, and application," *IEEE Trans. on Industrial Electronics*," vol. 49, no. 4, p.p. 724-738, August 2002.

- [3] E. Babaei, "A cascade multilevel converter topology with reduced number of switches", *IEEE Trans. on Power Electronics*, vol. 23. no. 6, p.p. 2657-2664, November 2008.

- [4] G. Ceglia, V. Guzman, C. Sanchez, F. Ibanez, J. Walter and M. I. Gimenez "A new simplified multilevel inverter topology for DC-AC conversion", *IEEE Trans. On Power Electronics*, vol. 21. no. 5, p.p. 1311-1319, September 2006.

- [5] G. Waltrich and I. Barbi, "Three-phase cascaded multilevel inverter using power cells with two inverter legs in series," *IEEE Trans. On Industrial Electronics*, vol. 57, no. 8, p.p. 2605-2612, August 2010.

- [6] D. Ruiz-Caballero, R. Sanhueza, H. Vergara, M. Lopez, M. L. Heldwein and S. A. Mussa, "Cascaded symmetrical hybrid multilevel DC-AC converter", *in Proc. of ECCE2010*, p.p. 4012-4019.

Fig. 5. Simulation result waveforms.

Fig. 6. Experimental test result waveforms.